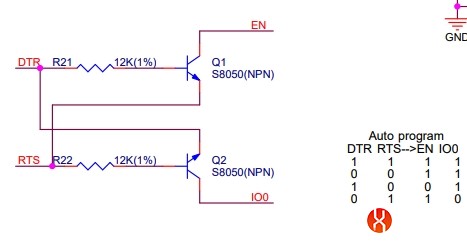

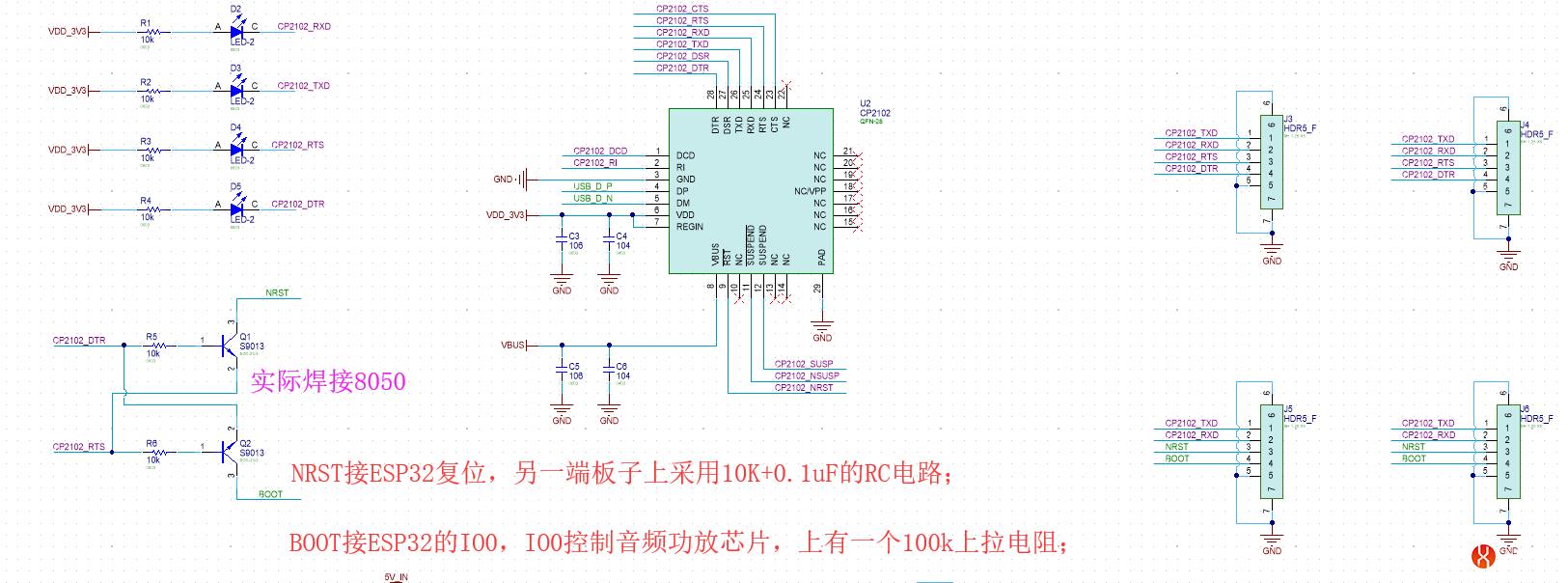

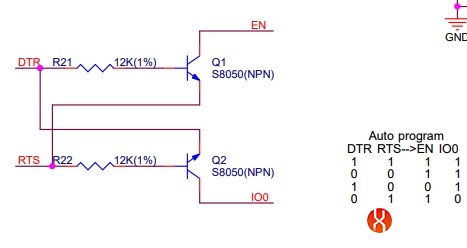

首先我按照官方的ESP32-Core-Board-V2_sch 原理图中的自动下载电路

绘制了一个自己的电路(自己的下载电路与官方的电路图完全一致)

在实际使用中发现如下情况:

- 使用自己的自动下载电路的ESP32板子

- 我自己的电脑,通过安信可的编译工具 Windows环境下,make flash后可以正常下载;

- 使用同事A的电脑(ubuntu 16.04)linux环境下 也一样可以下载;

- 使用同事B的电脑(ubuntu 18.04)Windows环境下 VMware虚拟机 就不可以下载(一直卡在等待链接的界面,等了近1分钟,直到失败)。

使用ESP32-Core-Board-V2开发板 以上三台电脑都可以正常下载!

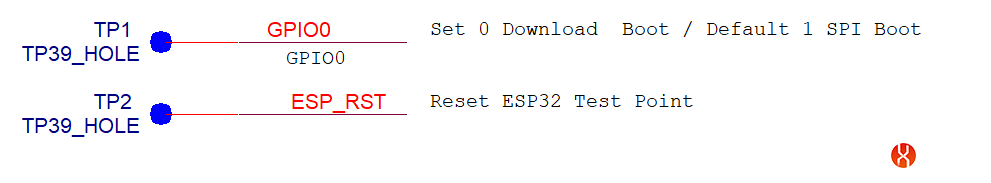

通过逻辑分析仪抓取自己的板子和ESP32-Core-Board-V2开发板 中的IO0和RST引脚,得出了一点差异!具体如下:

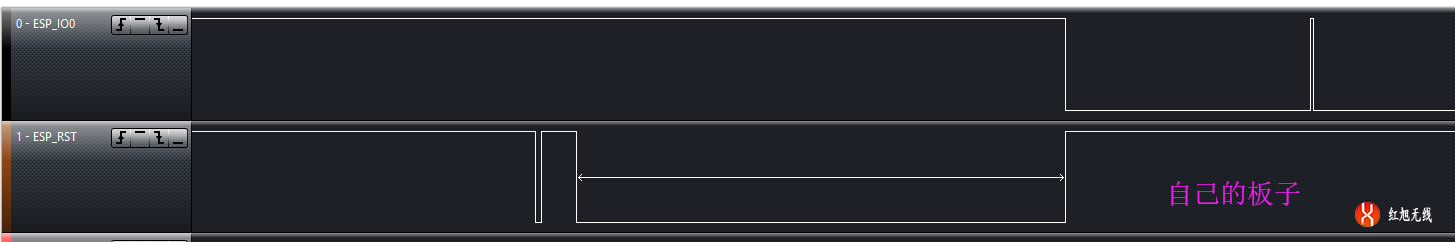

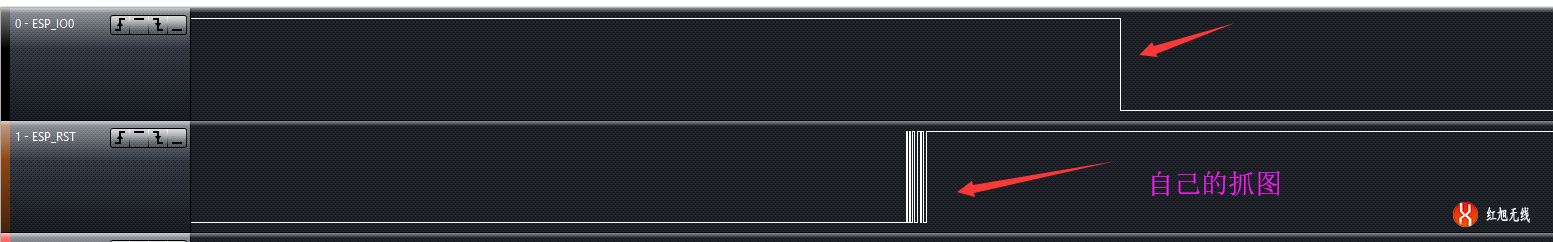

- 通过自己的电脑测试,抓取自己开发板的IO0和RST引脚,波形如图

- 测试发现RST引脚先拉高,过一会后 IO0才被拉低,按理说这个达不到芯片数据手册描述的需要IO0 = 0情况下复位芯片才进入下载模式的说法,但是为何自己的板子自己的电脑和同事A的电脑可以下载无法解释!

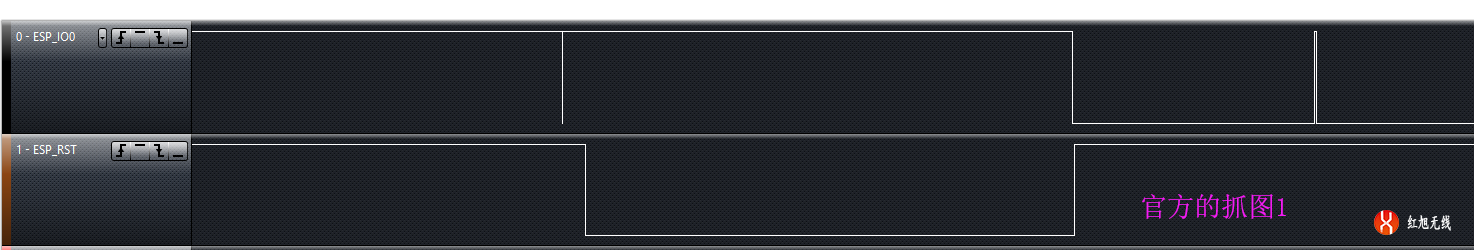

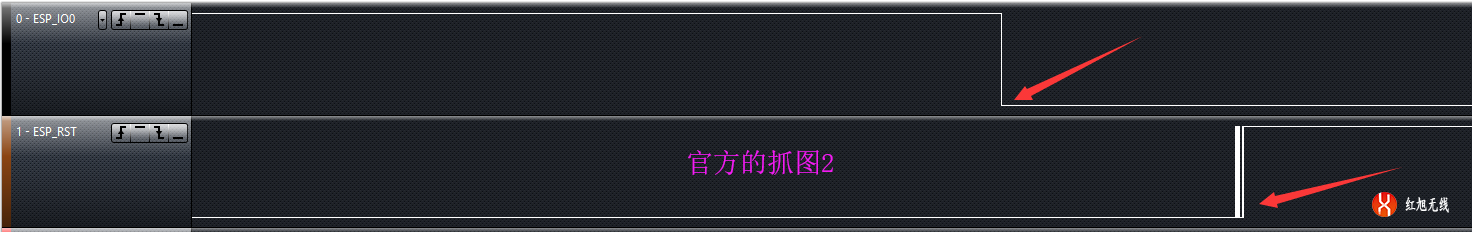

- 通过自己的电脑测试,抓取ESP32-Core-Board-V2开发板的IO0和RST引脚,波形如图

测试发现IO0引脚先拉低,过一会后RST引脚才被拉高,按理说这个才是芯片数据手册描述的需要IO0 = 0情况下复位芯片才进入下载模式的!

同样的两个下载电路,但是出现不同的现象,我对此表示很奇怪,请有遇到过该问题的朋友指导下,谢谢!